# **ISL54228IRTZEVAL1Z Evaluation Board User Manual**

# **Description**

The ISL54228IRTZEVAL1Z evaluation board is designed to provide a quick and easy method for evaluating the ISL54228 USB Switch IC.

The ISL54228 device is a unique IC. To use this evaluation board properly, requires a thorough knowledge of the operation of the IC. See the ISL54228 datasheet for an understanding of the functions and features of the device. Studying the device's truth-table along with its pinout diagram on page 2 of the datasheet is the best way to get a quick understanding of how the part works.

A picture of the evaluation board is shown in Figure 1. The ISL54228 TDFN IC is soldered onto the evaluation board. It is located in the center of the board and is designated as U1.

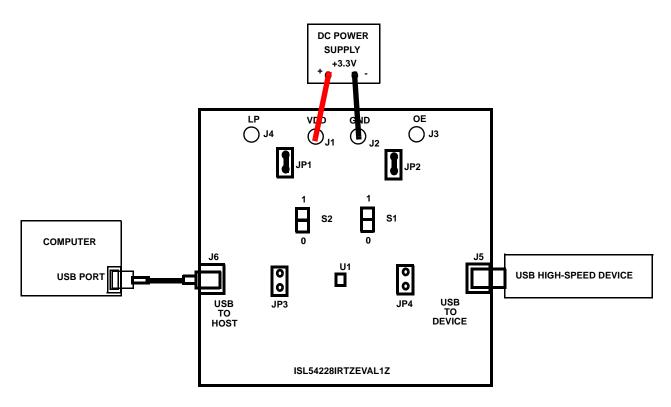

The evaluation board contains USB connectors, banana jacks, and toggle switches to allow the user to easily interface with the IC to evaluate its functions, features, and performance. For example, with the board properly powered and configured as shown in Figure 2 you can control the logic pins with the toggle switches, S1 (OE) and S2 (LP), to connect and disconnect the USB device from the USB host (computer).

In a typical application, the ISL54228 dual SPST part is used for switching or isolating a USB source in portable powered products.

This application note will guide the user through the process of configuring and using the evaluation board to evaluate the ISL54228 device.

## **Evaluation Board Photo**

FIGURE 1. ISL54228IRTZEVAL1Z EVALUATION BOARD

# **Key Features**

- · Standard USB connectors

- · Banana jacks for power, ground and logic input

- · Toggle switches for easy control of the logic pins

- · Convenient test points and connections for test equipment

# **Board Architecture/Layout**

## **Basic Layout of Evaluation Board**

The basic layout of the evaluation board is as follows: Refer to Figure 1 or the "ISL54228IRTZEVAL1Z Board Schematic" on page 4.

- Power and Ground connections are at banana jacks J1 (VDD) and J2 (GND) located at the top of the board.

- Logic input connections are at banana jacks J3 (OE) and J4 (LP) located at the top of the board or by using the toggle switches S1 and S2. Jumpers JP1 and JP2 must be installed to use the toggle switches. To control the logic through the banana jacks (J3 and J4) the JP1 and JP2 jumpers must not be populated.

- USB connection to an upstream host controller (Computer) is made at the USB connector J6 (USB TO HOST), located at the left side of the board.

- USB connection to the downstream USB device is made at USB connector J5 (USB TO DEVICE), located on right side of the board.

- The ISL54228 IC (U1) is located in the center of the board.

The evaluation board has a Pin 1 indicator dot to show how the IC should be oriented on the evaluation board. The IC Pin 1 indicator dot should be aligned with the evaluation board Pin 1 indicator dot.

### **IC Power Supply**

A DC power supply connected at banana jacks J1 (VDD) and J2 (GND) provides power to the ISL54228 IC. The IC requires a 2.7VDC to 5.25VDC power supply for proper operation. The power supply should be capable of delivering  $500\mu\text{A}$  of current.

## **Logic Control**

The state of the ISL54228 device is determined by the voltage at the LP pin and the OE pin. Access to the LP pin is through the banana jack J4 (LP) or the toggle switch S2. Access to the OE pin is through the banana jack J3 (OE) or the toggle switch S1. To use the toggle switches to control the logic, jumpers must be installed at JP1 and JP2. Remove jumpers to control the logic through the banana jacks.

If OE is driven "HIGH" (pulled up to VDD) and LP = "LOW" (to ground) with the signal voltage in the range of OV to 3.6V, the SPST switches will be ON. The USB host controller (computer) connected at J6 (USB TO HOST) will be connected

## **Application Note 1722**

through to the USB device connected at J5 (USB TO DEVICE) and data will be transmitted between the computer and the device.

If OE is driven "LOW" (to ground) and LP = "LOW" (to ground) with the signal voltage in the range of OV to 3.6V, the SPST switches will be OFF. The USB host controller (computer) connected at J6 (USB TO HOST) will be disconnected from the USB device connected at J5 (USB TO DEVICE) and no data will be transferred.

If OE = "LOW" and LP = "HIGH" the switches will be OFF and the part will be put in the low power state. In the low power state the part draws only 5µA (typ) of IDD current.

If the signal at the host (computer side) of the switch is >3.8V (typ) or ≤0.45V (typ) the ISL54228 IC will turn the switches OFF.

#### **USB Connections**

A "B" type USB receptacle labeled "USB TO HOST" (J6) is located at the right side of the board. This receptacle should be connected, using a standard USB cable, to the upstream USB host controller, which is usually a PC computer or hub.

An "A" type USB receptacle labeled "USB TO DEVICE" (J5) is located on the right side of the board. A USB device can be plugged directly into this receptacle or through a standard USB

The USB switches are bidirectional, which allows the host (computer) and downstream USB device to both send and receive data.

## **High-Speed Switches**

The two SPST switches are bidirectional switches that can pass signals up to 3.6V with a V<sub>DD</sub> supply voltage in the range of 2.7V to 5.25V.

When powered with a 2.7V supply, these switches have a nominal  $r_{\mbox{ON}}$  of 3.5  $\!\Omega$  over the signal range of OV to 400 mV with a  $r_{\mbox{ON}}$  flatness of 0.26  $\!\Omega\!.$  The  $r_{\mbox{ON}}$  matching between the SPST switches over this signal range is only 0.2 $\Omega$  ensuring minimal impact by the switches to USB high speed signal transitions. As the signal level increases, the ron switch resistance increases. At signal level of 3.3V the switch resistance is nominally 6.8 $\Omega$ .

The SPST switches were specifically designed to pass USB 2.0 high-speed (480Mbps) differential signals typically in the range of OV to 400mV. They have low capacitance and high bandwidth to pass the USB high-speed signals with minimum edge and phase distortion to meet USB 2.0 high-speed signal quality specifications.

The SPST switches can also pass USB full-speed signals (12Mbps) with minimal distortion and meet all the USB requirements for USB 2.0 full-speed signaling.

The maximum normal operating signal range for the SPST switches is from 0V to 3.6V. For normal operation, the signal voltage should not be allowed to exceed this voltage range or go below ground by more than -0.3V.

However, in the event that a positive voltage > 3.8V (typ) to 5.25V, (such as the USB 5V V<sub>BUS</sub> voltage) gets shorted to one or both of the (COM+ and COM-) pins or a negative voltage ≤0.5V (typ) to -5V gets shorted to one or both of the COM pins, the ISL54228 has overvoltage protection (OVP) circuitry to detect the overvoltage condition and open the SPST switches to prevent damage to the USB down-stream transceiver connected at the signal pins (D+ and D-).

The OVP and power-off protection circuitry allows the COM pins (COM-, COM+) to be driven up to 5.25V while the V<sub>DD</sub> supply voltage is in the range of OV to 5.25V. In this condition, the part draws <100µA of I<sub>COMx</sub> and I<sub>DD</sub> current and causes no stress to the IC. In addition, the SPST switches are OFF and the fault voltage is isolated from the other side of the switch.

## **Board Component Definitions**

Evaluation board components and their functions are shown in Table 1.

**TABLE 1. BOARD COMPONENT DESCRIPTIONS**

| DESIGNATOR | DESCRIPTION                         |

|------------|-------------------------------------|

| U1         | ISL54228IRTZ IC                     |

| J6         | "B" type USB Receptacle             |

| J5         | "A" type USB Receptacle             |

| J1         | VDD Positive Connection             |

| J2         | VDD Negative Connection             |

| J3         | OE Logic Control                    |

| J4         | LP Logic Control                    |

| S1         | OE Toggle Switch                    |

| S2         | LP Toggle Switch                    |

| JP1        | Toggle Switch S1 (OE) Jumper        |

| JP2        | Toggle Switch S2 (LP) Jumper        |

| JP3, JP4   | D-/D+ Differential Probe Connection |

FIGURE 2. BASIC EVALUATION TEST SETUP BLOCK DIAGRAM

# Using the ISL54228IRTZEVAL1Z Evaluation Board (see Figure 2)

#### **Lab Equipment**

The equipment, external supplies and signal sources needed to operate the board are listed as follow:

- 1. +2.7V to +5.25V DC Power Supply

- 2. One High-Speed USB device (i.e. USB memory stick, MP3 Player, etc.)

- 3. Computer with 2.0 High-Speed USB Port

- 4. Standard USB Cable

#### **Initial Board Setup Procedure**

- Install jumpers at JP1 and JP2. Allows logic control from S1 and S2 toggle switches.

- Attach the main evaluation board to a DC power supply at J1 (VDD) and J2 (GND). Positive terminal at J1 and negative terminal at J2. The supply should be capable of delivering 2.7V to 5.25V and 500μA of current. Set the supply voltage to 3.3V.

- Connect the high-speed USB device at USB connector J5.

This connector is located on the right side of the evaluation hoard

- 4. Drive the LP control pin LOW by putting toggle switch S2 (LP) in the down position.

- Drive the OE control pin LOW to open the SPST switches of the ISL54228 IC by putting toggle switch S1 (OE) in the down position.

- Connect USB cable from host (PC computer) to the USB "B" type receptacle, J6 (USB TO HOST).

### **High-Speed Operation**

- 1. Apply a logic LOW to the LP pin by putting toggle switch S2 (LP) in the down position.

- 2. Apply a logic HIGH to the OE pin by putting toggle switch S1 (OE) in the up position.

- 3. You should now be able to send and receive data between the computer and the USB device connected at J5.

- To disconnect the USB device from the computer take the OE pin LOW by putting toggle switch S1 (OE) in the down position.

#### **Low Power Operation**

- Apply a logic LOW to the OE pin by putting toggle switch S1 (OE) in the down position.

- 2. Apply a logic HIGH to the LP pin by putting toggle switch S2 (LP) in the up position.

- 3. The part will now be in the low power state. The IDD current will drop from 23μA (typ) to 5μA (typ).

# **Application Note 1722**

#### **Test Points**

The board has various test points to allow the user to connect probes to make measurements. The test points are described in Table 2.

TABLE 2.

| DESIGNATOR | DESCRIPTION                |

|------------|----------------------------|

| TP1        | V <sub>DD</sub> test point |

| TP2        | Ground Test Point          |

| TP3        | OE Test Point              |

| TP4        | LP Test Point              |

| TP5        | VBUS Test Point            |

**TABLE 2. (Continued)**

| DESIGNATOR | DESCRIPTION                                                        |

|------------|--------------------------------------------------------------------|

| JP3        | D-/D+ Differential Probe Connection - COM Side of Switch           |

| JP4        | D-/D+ Differential Probe Connection - USB Device<br>Side of Switch |

You can observe the D- and D+ USB signal at the device side of the switch on an oscilloscope or other test equipment by connecting a differential probe at JP4.

You can observe the D- and D+ USB signal at the COM side of the switch on an oscilloscope or other test equipment by connecting a differential probe at JP3.

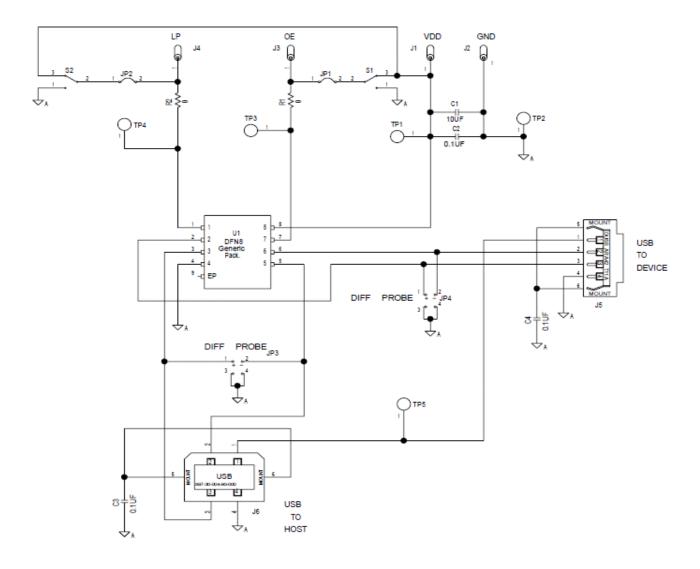

# ISL54228IRTZEVAL1Z Board Schematic

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com